## Name:

## Lab for ITSC 3181, Introduction to Computer Architecture, Spring 2023

Lab #10: Logic design using Digital (<u>https://github.com/hneemann/Digital</u>): Memory (SRAM) created using register files. Due 04/05 and count for 1% of the final accumulated grade.

From Lab 07 to Lab 12, you will build a RISC-V CPU to support an essential set of instructions including at least add, and, or, sub, lw, sw, and beq instructions. While you are encouraged to design a 32-bit CPU (each register stores a 32-bit word, and the ALU operates on 32-bit data), you are ok to design 8-bit or 16-bit CPU (each register stores a 8-/16-bit data, and the ALU operates on 8/16 bits data). Designing 8-bit/16-bit is much easier comparing with designing 32-bit, but with same design principle. But regardless of the bitwidth you use, each instruction is still encoded as a 32-bit word and the address for accessing data from memory are also 32-bit address. In this lab, we will create a simple 256 x 32/16/8-bit memory module using the register file we create in Lab09. It is actually a DRAM.

- Review lecture slides (145 146 of <u>https://passlab.github.io/ITSC3181/notes/AppendixA\_LogicDesignBasics.pdf</u>) for the design of a memory module that uses tristate buffer and a decoder to select memory cell to read/write.

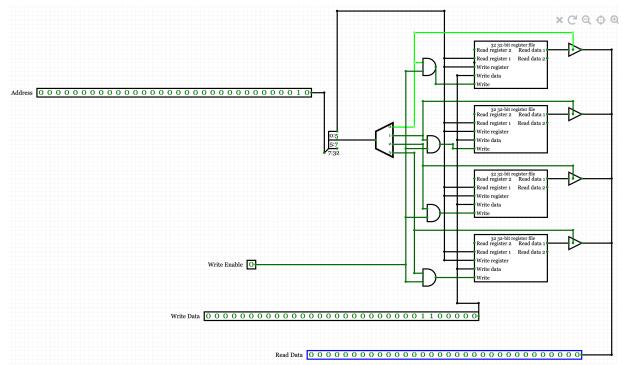

- 2. You will use the register file you designed in Lab09 to create a 256 x 32/16/8-bit memory module (256 rows and 32/16/8-bit width), which would require 8 register files you created before (256 = 8 \* 32). Below is the design of a 128 x 32bit memory module that uses 4 register files. Your design should be exactly like this, but have 8 register files for 256 rows. The input and output of the 256 x 32/16/8-bit module should be exactly the same as the following 128 x 32bit memory module. The inputs are 32-bit "Address", 1-bit "Write Enable", and 32/16/8-bit "Write Data". The output is 32/16/8-bit "Read Data".

- 3. It is important for you to understand the address of the memory module and how it is used to access a row of the memory. Given a 32-bit address, the least-significant 5 bits (bit 0-4) are used to select a row, which is a specific register within a register file, and next two bits (bit 5-6, and since we have four register files) is used to select a register file from the four files using a 4-1 decoder. The rest of the 32-bit address are ignored. The splitter in the following design shows how bits are split and fed into the right component of the design.

## Tasks:

- 1. (10%) Create a new circuit and save it as "256 x <bitwidth>-bit Memory". Arrange 8 register files for the 256 x 32/16/8-bit memory module by reusing the 32 32/16/8-bit RegisterFile you have designed before. Leave space between register files for wires.

- (10%) Add and label the inputs (32-bit "Address", 1-bit "Write Enable", and 32/16/8-bit "Write Data"), and the output (32/16/8-bit "Read Data"). Make sure the bitwidth and label are correctly set for them. Organize them in the appropriate position for the overall layout of the circuit. Connect the "Write Data" input to the "Write Data" input of all register files.

- 3. (10%) Since we have 8 register files, we need an 8-1 decoder to select one of the register files for read/write. Add a decoder in your design and set it to have the correct bitwidth for an 8-1 decoder.

- 4. (20%) Add a splitter to split the 32-bit address input into three parts, the least 5 bits go to "Read register 1" and "Write Register" of all registers, the next 3 bits go to the input of the decoder and ignore the rest.

- 5. (20%) Add an AND gate for each of the register files, and connect the two inputs of the AND gate to the corresponding decoder output and the "Write Enable" input. Connect the output of the AND gate to the "Write" input of the register file.

- 6. (20%) Add a trigate buffer (Wire→Driver) for each of the register file; and connect "Read data 1" output of the register file to the input of the trigate, connect the corresponding output of the decoder to the "Enable" input of the trigate, and connect the output of the trigate to the "Read Data" output of the memory module.

- 7. (10%) Test the "256 x 32/16/8-bit Memory" you designed: Simulate and test your memory design by setting address, write signal, read data and write data to make sure it works properly.

Important: when designing the circuit, please make sure you follow these rules for adding, changing components, input/output and wires. These rules are applied to all the design lab tasks of the course.

- 1) Each input and output of a design MUST be properly and meaningfully labeled.

- 2) Each component, input and output should be correctly configured in terms of its bitwidth and signal control width.