| Full Name: Ne | tID: _ |

|---------------|--------|

|---------------|--------|

## Final Exam 12/07/2016

OAKLAND UNIVERSITY, School of Engineering and Computer Science CSE 564: Computer Architecture, Fall 2016

Please write and/or mark your answers clearly and neatly; answers that are not readable are not considered. Please answer in appropriate details if needed and you may get partial points for the intermediate steps even if a final answer is not correct.

1. A program has two parallel portions, and one sequential portion. The two parallel portions make 30% and 40% of program respectively. If executing the program on a CPU with 4 cores, the speedups for the two parallel portions are 3 and 4. What is the overall speedup of the program? (4 points)

Speedup = 1/(0.3 + 0.3/3 + 0.4/4) = 2.

Suppose a processor executes at 200MHz clock rate (5 ns per cycle) with ideal CPI = 1. A program contains 40% arith/logic instructions, 50% ld/st, 10% control transfer instructions. If the miss rate for data cache is 0.1 and for instruction cache 0.02, both with 50 cycles miss penalty. What is the average CPI of the program? (6 points)

CPI = ideal CPI + average stalls per instruction = 1(cycles/ins) + [ 0.50 (DataMops/ins) x 0.10 (miss/DataMop) x 50 (cycle/miss)] + [ 1 (InstMop/ins) x 0.02 (miss/InstMop) x 50 (cycle/miss)] = (1 + 2.5 + 1) cycle/ins = 4.5

3. 1). Name the four kinds of cache misses and the three goals that most of the cache optimization techniques attempt to improve. 2). What kind of miss prefetching (software or hardware) would reduce the most? 3). In the multiple-level cache design, which goal is the L1-cache designed mainly for? Which goal is the L2 or L3 cache is mainly designed for? (10 points)

Misses: Compulsory, conflict, capacity and coherence Goals: Miss rate, miss penalty and hit time.

Compulsory miss

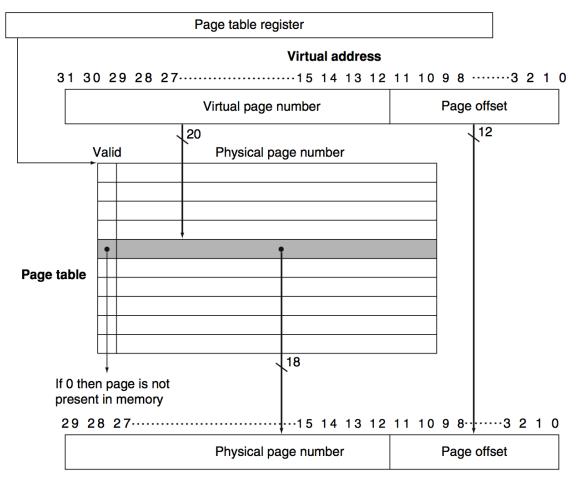

L1: reduce hit time; L2/L3: reduce miss rate 4. For following page table configuration for a 32-bit machine that has 4Kb page size and 256Mbyte of physical memory, the page table size (each page table entry is rounded to 2<sup>x</sup> bits which is 32 bit) is 4 bytes \* 2<sup>20 =</sup> 2<sup>22</sup> bytes = 4Mbytes. What is the page table size if the physical memory is 64Mbytes? (5 points)

## **Physical address**

64Mbyte/4K = 2<sup>(26–12)</sup> = 2<sup>14</sup> pages, thus we need 14 bits for physical page number, plus one valid bit, we need 15 bits (rounded up to 16 bits) per page entry. Thus the page table size is

2 bytes \* 2<sup>20 =</sup> 2<sup>21</sup> bytes = 2MBytes

5. What is the purpose of TLB? (5 points)

6. Fill in the following table for the three kinds of dependencies (5 points)

| 1. | DIV.D | F0, F2, F4   |

|----|-------|--------------|

| 2. | ADD.D | F6, F0, F8   |

| 3. | S.D   | F6, 0(R1)    |

| 4. | SUB.D | F8, F10, F14 |

| 5. | MUL.D | F6, F10, F8  |

| Dependency type | Register involved | 1 <sup>st</sup> Instruction | 2 <sup>nd</sup> instruction |

|-----------------|-------------------|-----------------------------|-----------------------------|

| RAW             | <mark>F0</mark>   | <mark>1</mark>              | 2                           |

| RAW             | <mark>F6</mark>   | 2                           | <mark>3</mark>              |

| RAW             | F8                | <mark>4</mark>              | <mark>5</mark>              |

| WAR             | F6                | <mark>3</mark>              | <mark>5</mark>              |

| WAW             | F6                | 2                           | <mark>5</mark>              |

The following C code, its corresponding assembly instructions, instruction latency table and the instruction-scheduling table will be used for questions 7 and 8.

| for   |                                      | i>=0; i=i-<br>= x[i] + s                                    | •                                                                                                                    |

|-------|--------------------------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| Loop: | L.D<br>ADD.D<br>S.D<br>DADDUI<br>BNE | F0,0(R1)<br>F4,F0,F2<br>F4,0(R1)<br>R1,R1,#-8<br>R1,R2,Loop | ;FO=array element<br>;add scalar in F2<br>;store result<br>;decrement pointer<br>;8 bytes (per DW)<br>;branch R1!=R2 |

For a machine with instruction latency as follows:

| Instruction producing result | Instruction using result | Latency in clock cycles |

|------------------------------|--------------------------|-------------------------|

| FP ALU op                    | Another FP ALU op        | 4                       |

| FP ALU op                    | Store double             | 3                       |

| Load double                  | FP ALU op                | 1                       |

| Load double                  | Store double             | 0                       |

The execution cycles (including stalls) of one iteration can be shown as follows:

| Instructions | Cycles          |

|--------------|-----------------|

| L.D          | <mark>1</mark>  |

| stall        | <mark>2</mark>  |

| ADD.D        | <mark>3</mark>  |

| stall        | <mark>4</mark>  |

| stall        | <mark>5</mark>  |

| stall        | <mark>6</mark>  |

| S.D          | <mark>7</mark>  |

| DADDUI       | <mark>8</mark>  |

| stall        | <mark>9</mark>  |

| BNE          | <mark>10</mark> |

Unroll the loops three times and apply instruction rescheduling so stall can be completely eliminated (assuming unlimited number of registers to use). Show the scheduling and cycle table similar to the above and calculate cycles per iteration of the original loop (to compute one element). (10 points)

| Answer:      |                 |

|--------------|-----------------|

| Instructions | Cycles          |

| LD           | <mark>1</mark>  |

| LD           | <mark>2</mark>  |

| LD           | <mark>3</mark>  |

| ADD          | <mark>4</mark>  |

| ADD          | <mark>5</mark>  |

| ADD          | <mark>6</mark>  |

| DADDUI       | <mark>7</mark>  |

| SD           | <mark>8</mark>  |

| SD           | <mark>9</mark>  |

| SD           | <mark>10</mark> |

| BNE          | <mark>11</mark> |

## Cycles per iteration = 11/3 = 3.67

Unroll the loops 10 times and schedule instructions to achieve minimum number of cycles of execution in a VLIW machine of which each VLIW can include two LD/ST operations, two FP operations and one integer ALU/branch operations. Please include your solution in the following scheduling table (not necessarily 16 cycles). (10 points)

| Cycles | LD/ST 1 | LD/ST 2 | FP 1 | FP 2 | Integer<br>ALU/Branch |

|--------|---------|---------|------|------|-----------------------|

| 1      |         |         |      |      |                       |

| 2      |         |         |      |      |                       |

| 3  |  |  |  |

|----|--|--|--|

| 4  |  |  |  |

| 5  |  |  |  |

| 6  |  |  |  |

| 7  |  |  |  |

| 8  |  |  |  |

| 9  |  |  |  |

| 10 |  |  |  |

| 11 |  |  |  |

| 12 |  |  |  |

| 13 |  |  |  |

| 14 |  |  |  |

| 15 |  |  |  |

| 16 |  |  |  |

|                     |                 |                 |                  |                  | <mark>Integer</mark> |

|---------------------|-----------------|-----------------|------------------|------------------|----------------------|

| <mark>Cycles</mark> | LD/ST 1         | LD/ST 2         | FP 1             | FP 2             | ALU/Branch           |

| <mark>1</mark>      | LD              | LD              |                  |                  |                      |

| <mark>2</mark>      | LD .            | LD              |                  |                  |                      |

| <mark>3</mark>      | LD              | LD              | <mark>ADD</mark> | ADD              |                      |

| <mark>4</mark>      | LD              | LD              | <mark>ADD</mark> | ADD              |                      |

| <mark>5</mark>      | LD .            | <mark>LD</mark> | <mark>ADD</mark> | ADD              |                      |

| <mark>6</mark>      |                 |                 | <mark>ADD</mark> | <mark>ADD</mark> |                      |

| <mark>7</mark>      | <mark>SD</mark> | <mark>SD</mark> | <mark>ADD</mark> | ADD              |                      |

| <mark>8</mark>      | <mark>SD</mark> | <mark>SD</mark> |                  |                  |                      |

| <mark>9</mark>      | <mark>SD</mark> | <mark>SD</mark> |                  |                  | <mark>DADDUI</mark>  |

| <mark>10</mark>     | <mark>SD</mark> | <mark>SD</mark> |                  |                  |                      |

| <mark>11</mark>     | <mark>SD</mark> | <mark>SD</mark> |                  |                  | BNE                  |

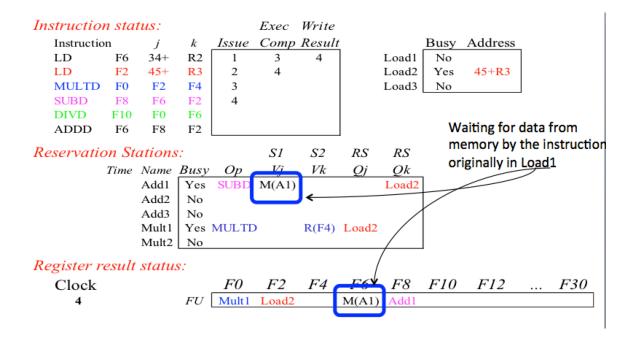

9. Explain how register renaming and out-of-order execution are achieved in the Tomasolu algorithm using the following diagram. (10 points)

- 10. Explain how does the reorder-of-buffer work for branch prediction and hardware speculation. (6 points)

- 11. Explain the differences between Coarse-Grained Multithreading, Find-Grained Multithreading and Simultaneous Multithreading. (6 points)

- 12. For a machine with max vector length 64, the following code

int N = 64; for (i=0; i<N; i++) Y[i] = a\* X[i] + Y[i];

can be vectorized as:

| L.D     | F0,a     | ;load scalar a          |

|---------|----------|-------------------------|

| LV      | V1,Rx    | ;load vector X          |

| MULVS.D | V2,V1,F0 | ;vector-scalar multiply |

| LV      | V3,Ry    | ;load vector Y          |

| ADDVV.D | V4,V2,V3 | ;add                    |

| SV      | V4,Ry    | ;store the result       |

If N is 96, write the assembly code for vectorizing the loop using strip mining technique with vector length register. The instructions for read/write the vector length register are as follows: (10 points)

| MTC1 | VLR,R1 | Move contents of R1 to vector-length register VL.     |

|------|--------|-------------------------------------------------------|

| MFC1 | R1,VLR | Move the contents of vector-length register VL to R1. |

Add R1, R0, 96 SUB R1, R1, 64 MTC1 VLR, R1 <<the above sequence>> ADD R1, R0, 64 MTC1 VLR, R1 <<the above sequence>>

- 13. For scheduling multiple threads in CPU, switching a thread on or off a CPU core involves restoring or storing the thread state (registers, PC, etc), which makes thread scheduling a costly operation. However, for GPU manycore thread scheduling, even threads are scheduled and executed in a warp group (32 threads), switching a warp of threads on and off GPU is very efficient. Explain what GPU feature makes this possible? (5 points)

- Explain the cache coherence problem in MIMD architecture, e.g. symmetric multiple processor systems and explain how write-invalidate cache snooping protocol works to provide cache coherence for parallel programs. (8 points)

- 15. In this question, you need to describe the false sharing problem and propose a software solution and a hardware solution. (Total 15 points bonus)

- 1). What is false sharing and how it is caused.

2). Using a program example to explain how to eliminate false sharing by padding.

3). From the architecture point view, please propose a solution in the cache architecture to eliminate false sharing.

----- The end of the Test -----

| Full Name: |  | NetID: |

|------------|--|--------|

|------------|--|--------|